| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- system

- DATAPATH

- php

- mysql

- data structure

- javascript

- while

- computer

- python

- DS

- Java

- for

- instruction

- XML

- DB

- Pipelining

- html

- Class

- web

- DoM

- Linux

- control

- architecture

- MacOS

- function

- github

- react

- CSS

- Algorithm

- MIPS

- Today

- Total

YYYEJI

[MIPS] Pipelining Hazard 본문

Hazard란?

Clock cycle이 증가함에 따라 잘 진행되야 하는데

다음 clock cycle에서 Instruction을 수행할 수 없는 상황을 의미합니다.

Pipelining에서는 3개의 hazard가 있습니다.

하나씩 살펴보겠습니다.

① Structural Hazard

Stage 1에서는 instruction을 fetch하고,

stage 4에서는 data를 read/write 해야하는데,

동시에 진행할 수 없는 상황을 의미합니다.

• MEM - IF: instruction, data를 한 번에 읽을 수 없다면 hazard 발생.

• EX - IF: 기본적인 연산인 add, sub etc를 계산하면서 PC의 값을 증가시킬 수 없다면 hazard 발생.

• WB - ID: Register에 값이 쓰이면서 읽힐 수 없다면 hazard 발생

Solution - resource를 여러 개 사용해서 구조적인 문제를 해결하자.

② Data Hazard

아래 상황과 같이 add에서 아직 수행된 값이 $S0에 저장되지 않았는데,

다음 instruction에서 $S0의 값이 읽혀져야 되는 상황을 의미합니다.

ADD $S0, $t1, $t2

SUB $S1, $S0, $t2

Solution 1 - Stall 시키자.

Solution 2 - Forwarding 시키자.

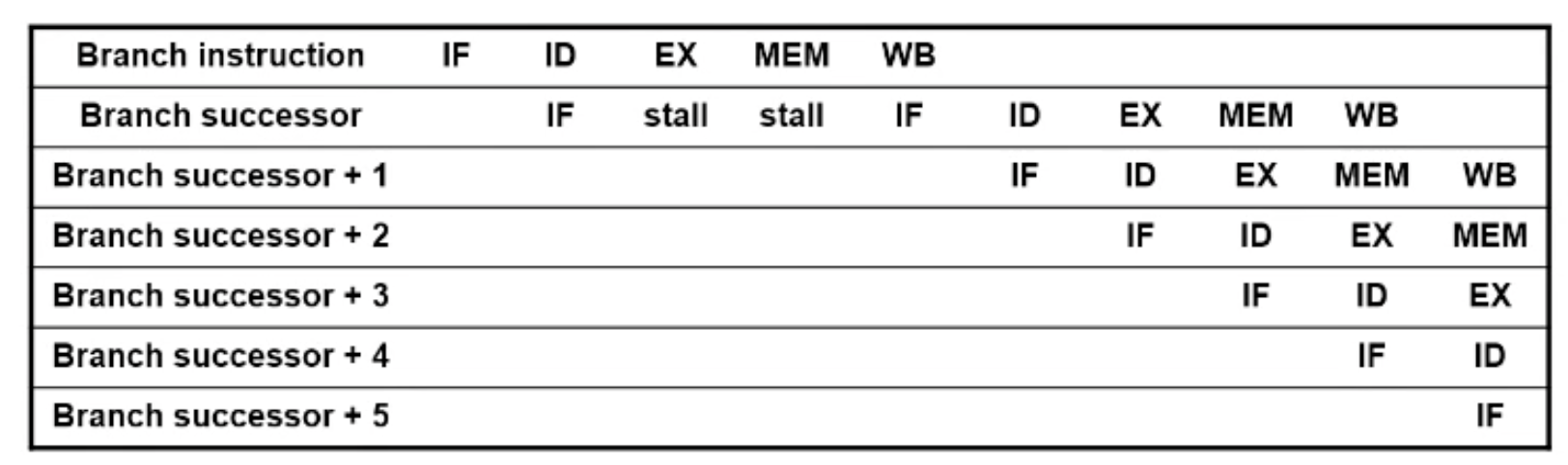

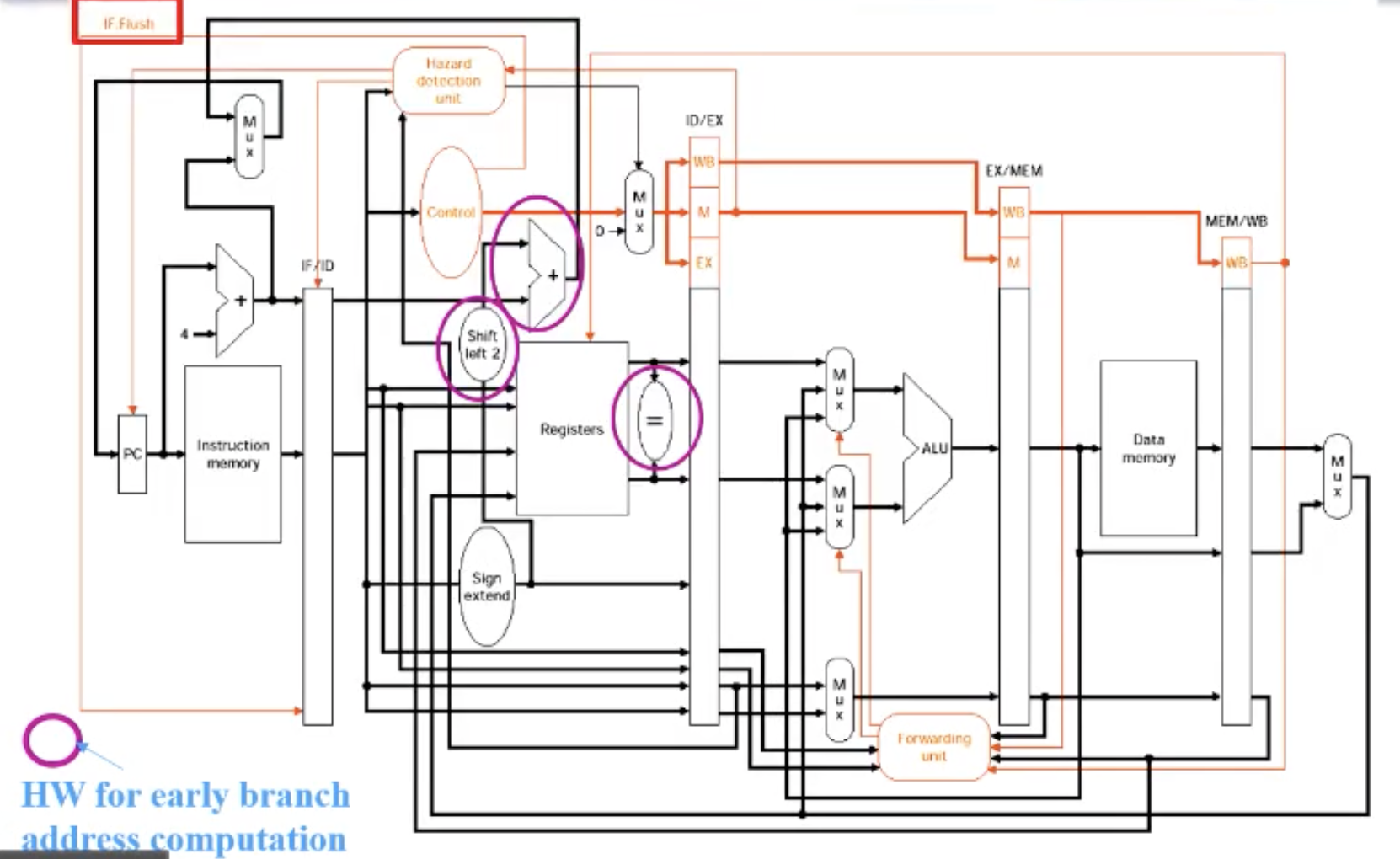

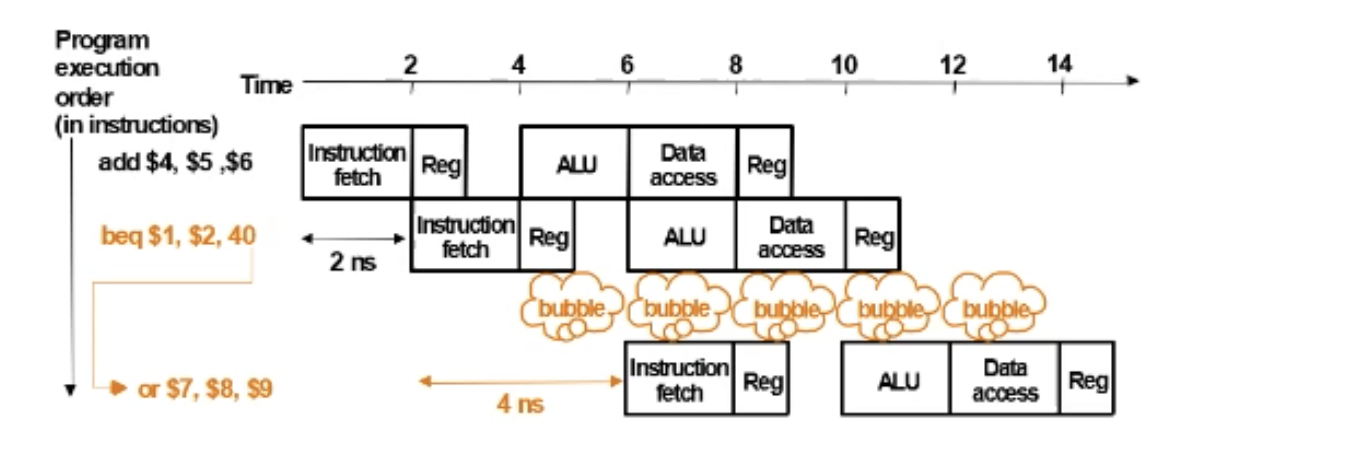

③ Control Hazard

beq instruction의 결과를 확인하지 전까지

다음 instruction을 수행하지 않고 기다리고 있는 상황을 의미합니다.

beq $t0, $t1, label

add ....................

sub ....................

label: and ....................

Solution 1 - Stall 시키자.

Solution 2 - Branch 유무를 빨리 결정하자.

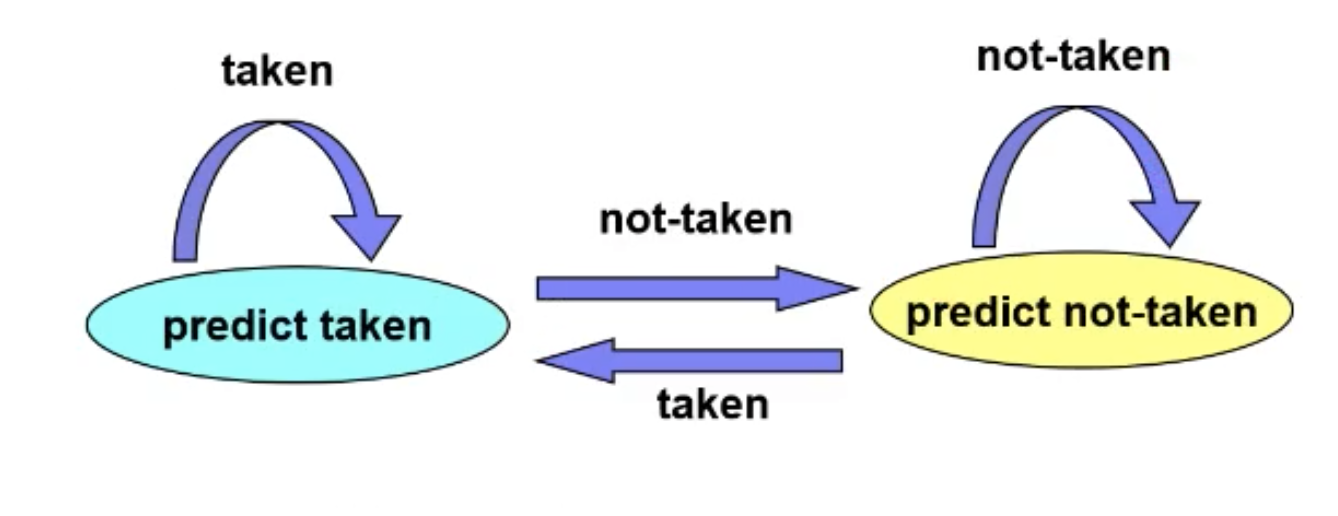

Solution 3 - Branch 유무를 예측하자.

• beq, never branch로 예측

• bne, always branch로 예측

1 bits 예측 메모리 두기

◡̈

'Computer architectures' 카테고리의 다른 글

| [MIPS] Memory hierarchy (locality) (0) | 2022.12.03 |

|---|---|

| [MIPS] Performance (0) | 2022.11.28 |

| [MIPS] Pipelining Control Signal (0) | 2022.11.27 |

| [MIPS] Corrected Datapath란? (0) | 2022.11.27 |

| [MIPS] beq Datapath (Pipelining) (0) | 2022.11.27 |