| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- DS

- system

- mysql

- instruction

- Java

- web

- XML

- function

- control

- html

- DoM

- python

- php

- Class

- DATAPATH

- while

- architecture

- MacOS

- github

- react

- computer

- data structure

- for

- Pipelining

- MIPS

- DB

- Algorithm

- Linux

- javascript

- CSS

- Today

- Total

YYYEJI

[MIPS] Multi Clock Cycle 본문

Single clock cycle의 단점을 보안한 clock cycle입니다.

single clock cycle의 의문점은

① Floating point처럼 복잡한 지시는 어떻게 해결할까 ?

② 같은 기능을 하는 하드웨어가 많이 필요할까 ?

입니다.

그렇게 나온 해결책이 MULTI-Clock-Cycle 입니다.

Multi-clock-cycle은 하드웨어를 줄인 finite state machines을 사용합니다.

- ALU(Arithmetic Logic Unit for Calculation, Adder for PC)

- Memory(Instruction memory, data memory)

- Register(Instruction register, Memory data register, A, B, ALUout)

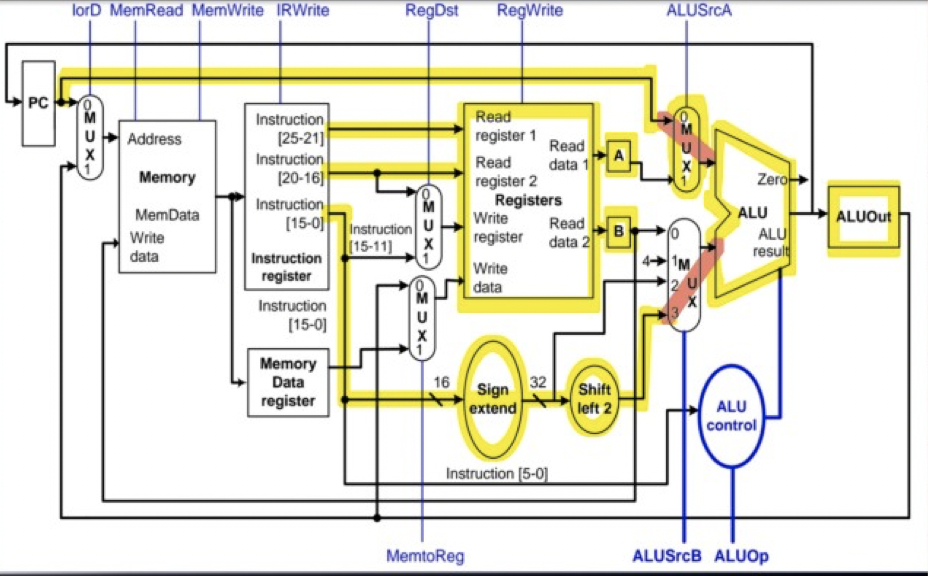

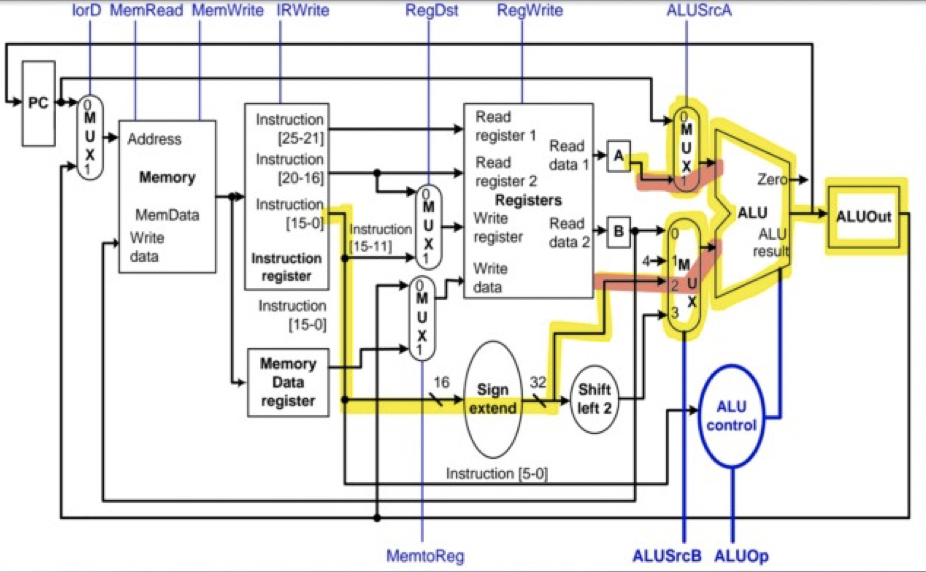

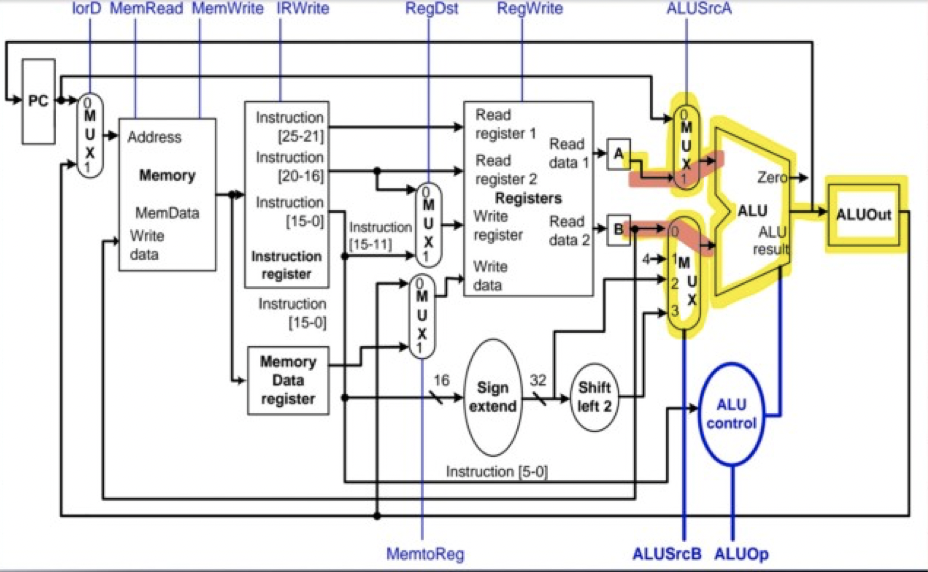

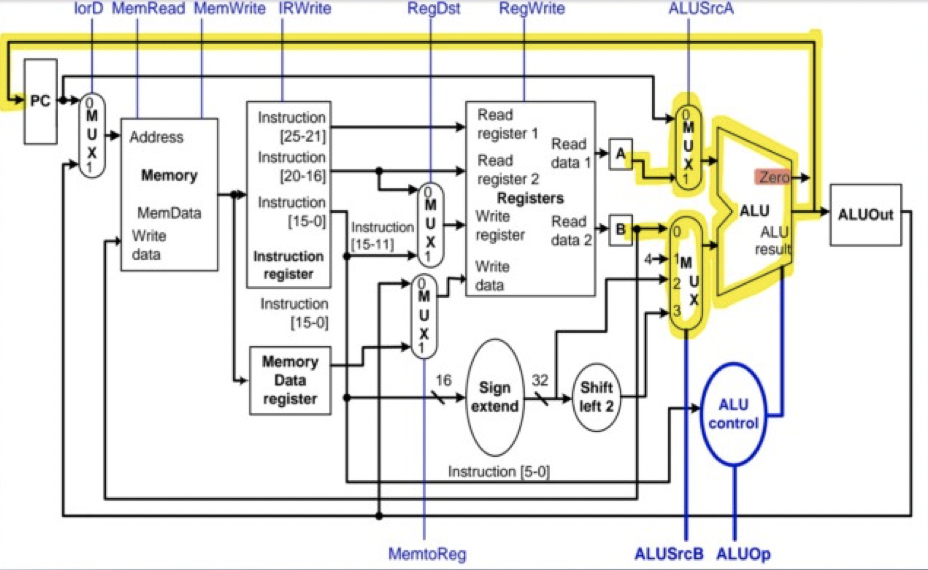

Five Execution Steps

Note) ALU를 사용하지 않을 때 미리미리 PC 계산, Label 계산 등을 미리 해둡니다.

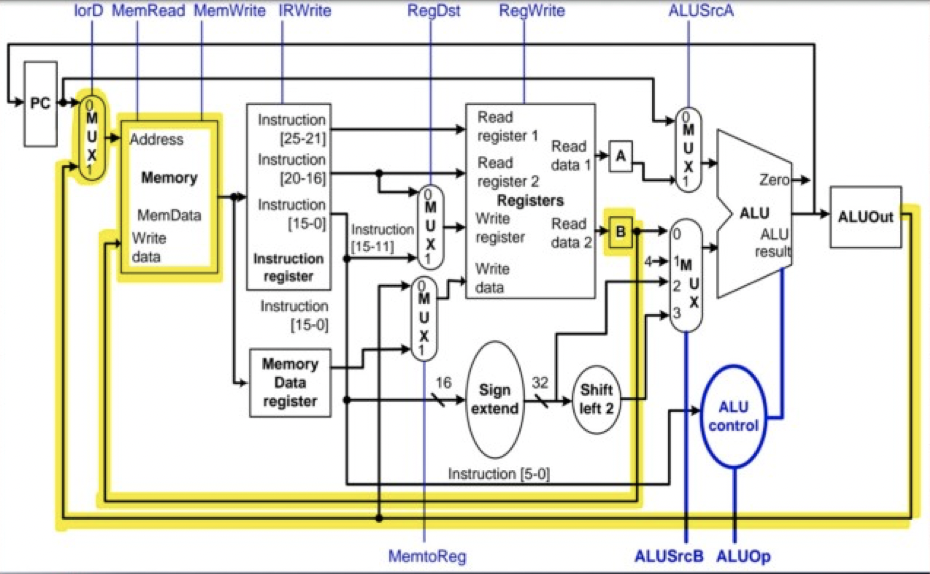

① Insturction fetch

• Memory에서 instruction을 fetch해와서 IR(intruction register)에 보관합니다.

IR ← Mem[PC];

PC ← PC + 4;

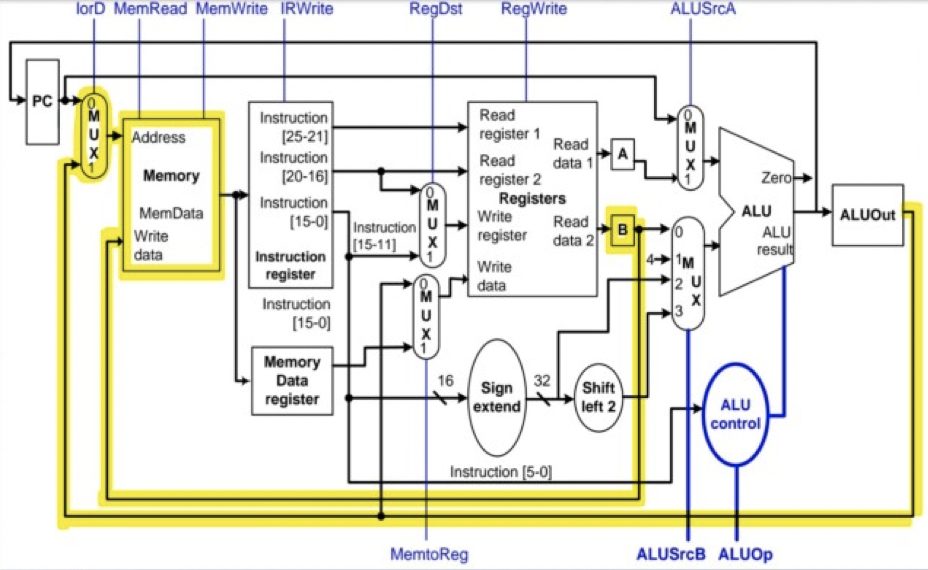

② Instruction Decode and Register Fetch

• Instruction과 instruction의 구조를 파악합니다.

• 그리고 필요한 register의 값을 읽습니다.

R-type의 예

A ← Reg[IR[25:21]];

B ← Reg[IR[20:16]];

ALUOut ← PC + (Sign-extend(IR[15:0] << 2);

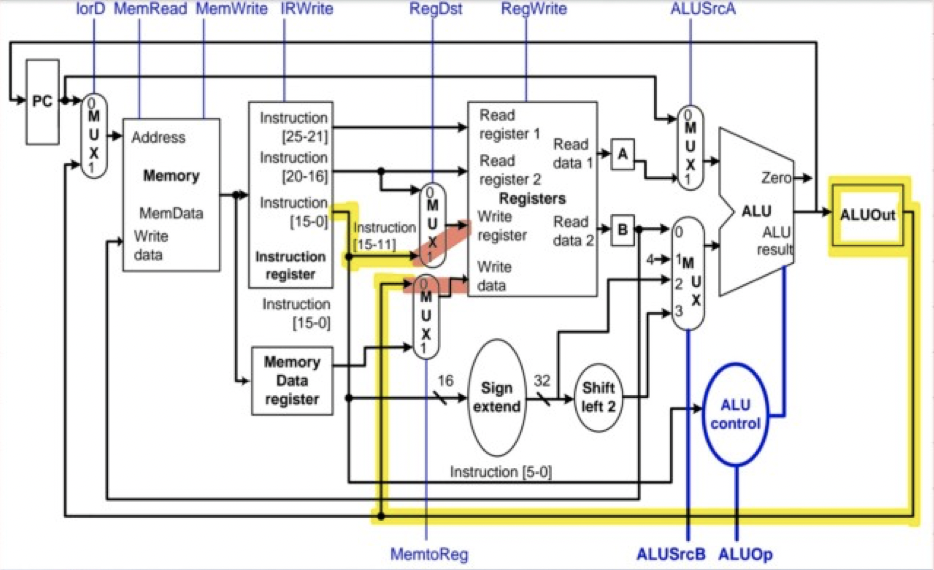

③ Execution(R-type), Memory Address Computation(lw, sw), Branch completion

• Fetch된 instruction에 따라 무언가를 수행합니다.

Memory Reference

ALUOut ← A + sign-extend(IR[15:0]);

R-type

ALUOut ← A op B;

Branch

if (A==B) PC ← ALUOut;

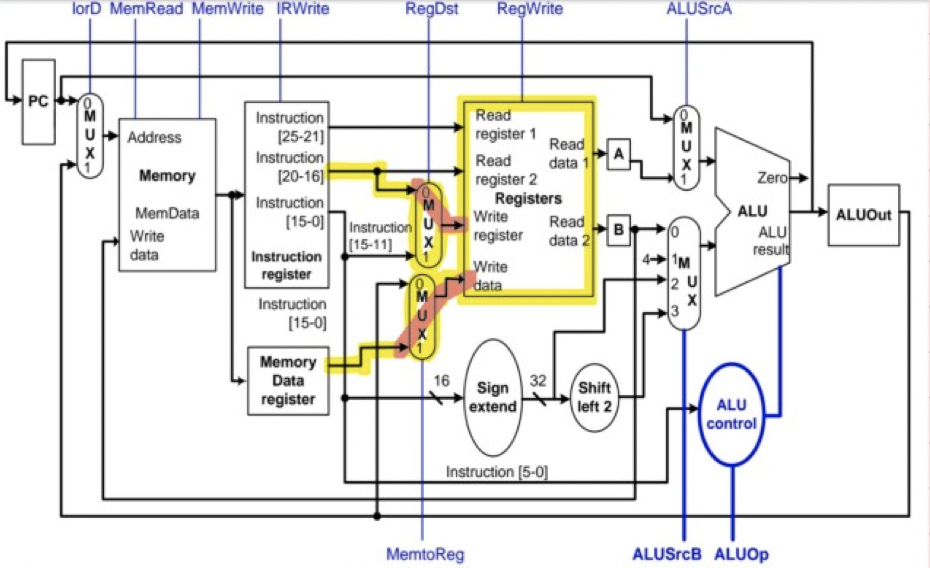

④ Memory Access(lw/sw), R-type instruction completion

• Fetch된 instruction에 따라 무언가를 수행합니다.

Loads and stores access memory

# lw

MDR ← Memory[ALUout];

# sw

Memory[ALUOut] ← B;

R-type instruction completion

Reg[IR[15:11]] ← ALUOut;

⑤ Write-back (lw)

Reg[IR[20:16]] ← MDR;

instruction 마다 실행되는 step 수가 다릅니다.

beq - 3 step

R-type, sw - 4 step

lw - 5 step

Note) Step1, Step2는 어떤 Instruction이든 실행됩니다.

◡̈

'Computer architectures' 카테고리의 다른 글

| [MIPS] Sequential Execution과 Parallel Execution (0) | 2022.11.12 |

|---|---|

| [MIPS] Pipelining (0) | 2022.11.12 |

| [MIPS] beq Control unit (Single-Clock) (0) | 2022.11.07 |

| [MIPS] sw Control unit (Single-Clock) (0) | 2022.11.07 |

| [MIPS] lw Control unit (Single-Clock) (0) | 2022.11.07 |