| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 |

- Linux

- DoM

- Java

- while

- react

- javascript

- DS

- system

- html

- php

- mysql

- Algorithm

- CSS

- instruction

- XML

- web

- MIPS

- Pipelining

- control

- python

- architecture

- MacOS

- data structure

- for

- github

- DB

- computer

- DATAPATH

- Class

- function

- Today

- Total

YYYEJI

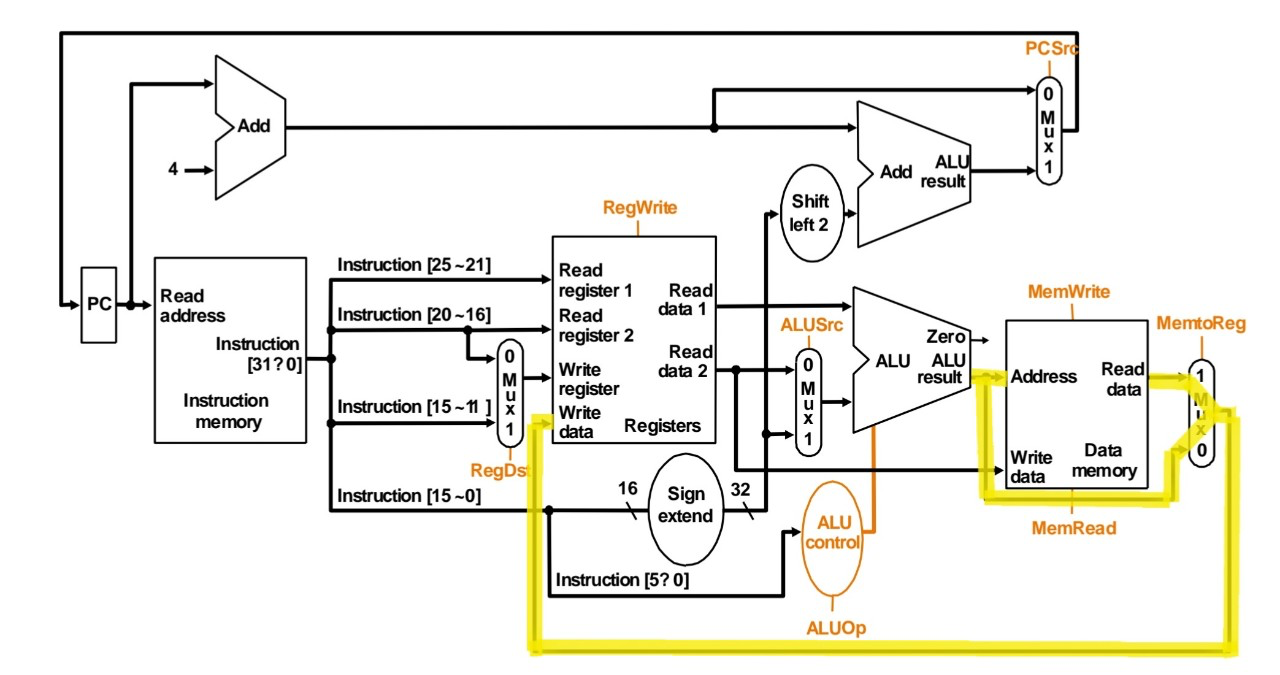

[MIPS] Control unit을 결정하는 Multiplexer (Single-Clock) 본문

[MIPS] Control unit을 결정하는 Multiplexer (Single-Clock)

YEJI ⍢ 2022. 11. 7. 15:35

각각의 unit이 어떤 일을 수행할지 결정하는 MUX(Multiplexer)가 존재합니다.

Multiplexer(MUX)는

여러 아날로그 또는 디지털 입력 신호 중 하나를 선택하여 선택된 입력을 하나의 라인에 전달하는 장치입니다.

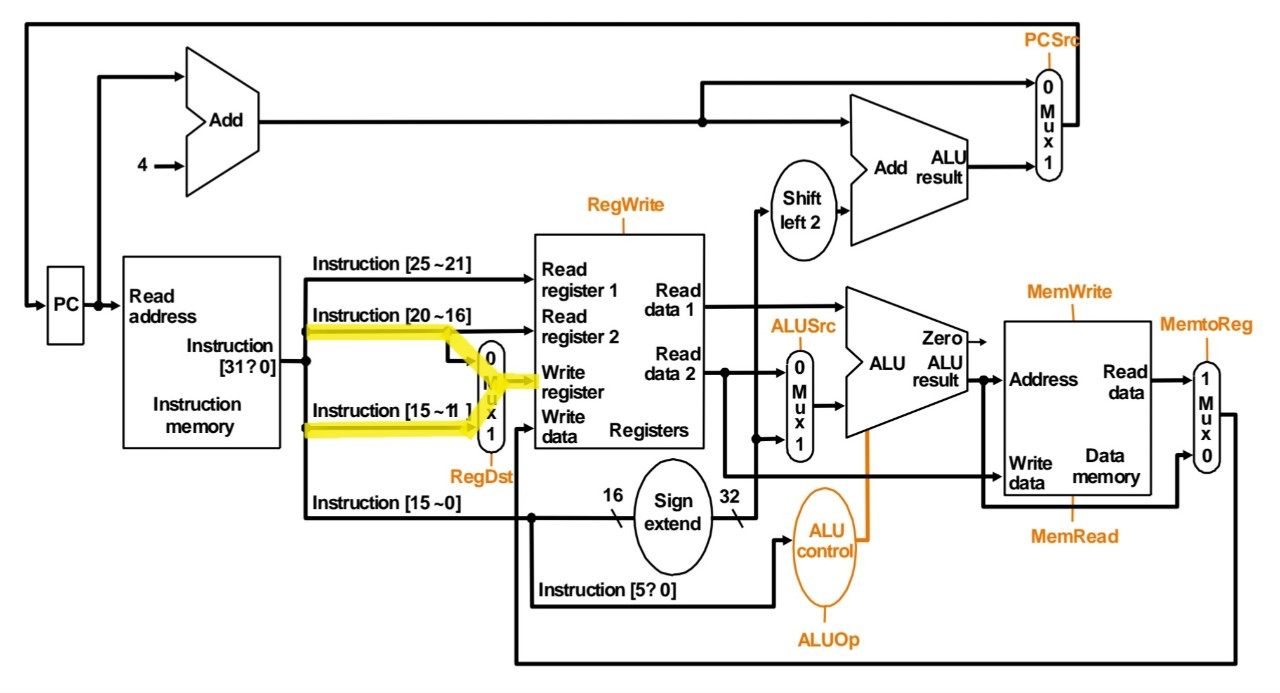

아래 사진에 4개의 MUX가 있습니다.

하나하나 살펴보겠습니다.

① RegDes - Register Destination

Instruction 어느 register에 값이 쓰일지 결정합니다.

RegDes는 instruction foramt이해가 필요합니다.

R-type instruction format

| Op code | rs | rt | rd | shamt | Function code |

| 31 26 | 21 | 16 | 11 | 6 | 0 |

• R-type의 destination은 rd이고, 15~11 bit에 존재합니다.

I-type instruction format

| Op code | rs | rt | Imme 16 |

| 31 26 | 21 | 16 | 0 |

• I-type의 destination은 rt이고, 20~16 bit에 존재합니다.

먼저 Register file에서 write register는 값이 쓰여질 register을 의미합니다.

R-type의 destination과 I-type의 destination이 다르기 때문에 MUX가 필요합니다.

즉, 15~11 bit에 destination이 존재하는 R-type은 MUX에서 1을 선택하게 되고,

20~16 bit에 destination이 존재하는 lw는 MUX에서 0을 선택합니다.

(sw는 memory에 값이 쓰이기 때문에 write register을 사용할 필요가 없습니다.)

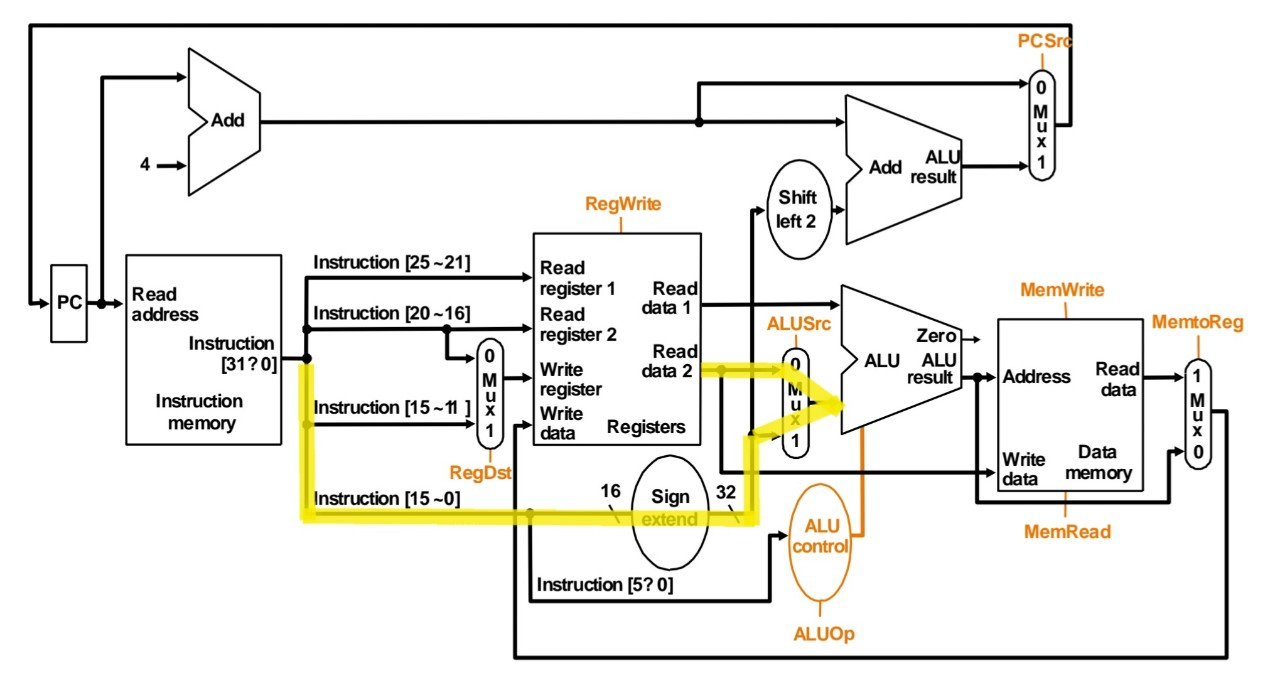

② ALUSrc - ALU Soruce

ALU에서 계산될 두 번째 데이터를 결정합니다.

R-type은 register에서 값을 읽어야되고,

I-type은 immediate value를 SignExt 시켜서 사용해야 됩니다.

즉 R-type은 register에서 읽은 값을 선택해야 되기 때문에 MUX에서 0을 선택하고,

lw, sw는 SignExt된 값을 선택하기 때문에 MUX에서 1을 선택합니다.

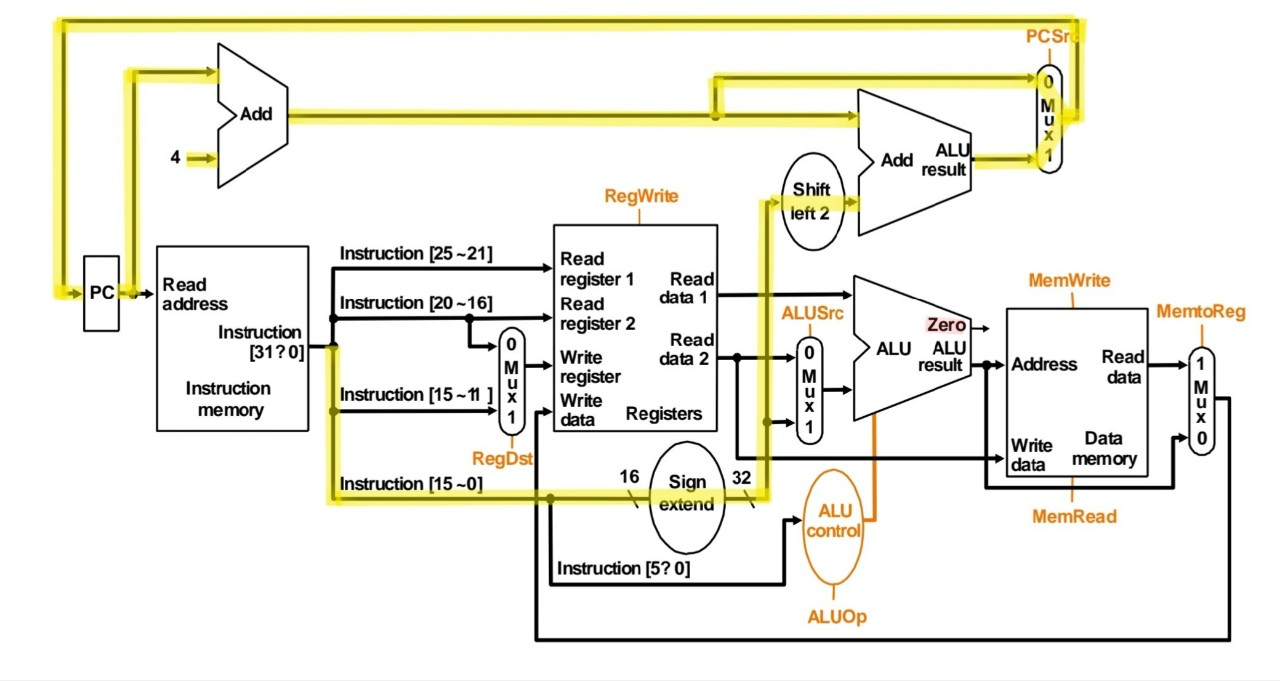

③ PCSrc - PC Source

PC의 값을 조정하는데 사용되는 MUX이고,

ALU 안에 있는 zero의 값에 따라 branch의 유무를 결정합니다.

beq(branch if equal)을 예로 들어보겠습니다.

beq $t0, $t1, label

• $t0와 $t1의 값을 읽고 ALU에서 두 개의 값을 빼줍니다.

• Zero에 값이 들어가게 되는데,

ALU 계산 결과가 0이면 zero에 1이 들어가면서 true 처리가 되어 branch를 하게 됩니다.

ALU 계산 결과가 non-zero가 나오면 zero에 0이 들어가면 false로 처리되어 branch를 하지 않습니다.

즉, True일 경우에는 MUX를 1로 선택해서 branch를 해주고,

False의 경우에는 MUX를 0으로 선택해서 PC+4만 한 값이 PC에 들어가게 됩니다.

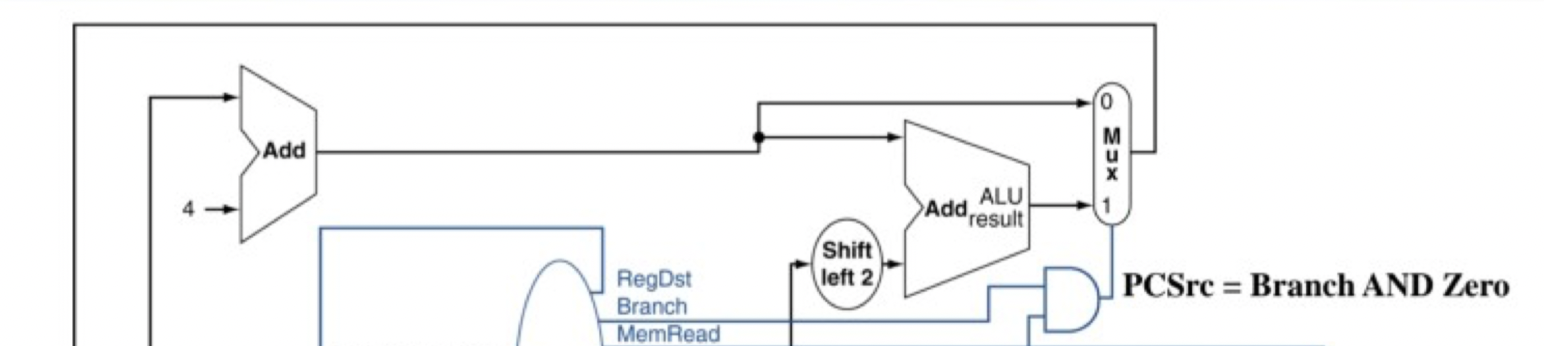

사실 PCSrc mux에 가기 전에 AND gate가 존재합니다.

Q) AND gate의 역할은 무엇일까요?

A) Instruction이 beq이면서 Zero의 값이 "1"임을 확인하는 gate입니다.

R-type instruction을 수행하는데 ALU 계산 결과가 "0"이 나와서

아무때나 branch를 수행하면 안 되기 때문입니다.

④ MemtoReg - Memory to Register

Resiter에 저장될 값을 결정하게 됩니다.

(Memory에서 읽은 데이터인지, ALU에서 수행된 데이터인지)

lw는 데이터를 memory에서 fetch해서 register에 저장하고,

R-foramt(add, sub, and, or, slt)는 수행된 값을 register에 저장합니다.

즉, lw는 data memory와 연결된 MUX 1을 선택하고,

R-type은 ALU의 결과가 연결된 MUX 0을 선택하게 됩니다.

◡̈

'Computer architectures' 카테고리의 다른 글

| [MIPS] lw Control unit (Single-Clock) (0) | 2022.11.07 |

|---|---|

| [MIPS] R-type Control unit (Single-Clock) (0) | 2022.11.07 |

| [MIPS] ALU를 control하는 signal (Single-Clock) (0) | 2022.11.07 |

| [MIPS] beq Datapath (Single-Clock) (0) | 2022.11.07 |

| [MIPS] sw Datapath (Single-Clock) (0) | 2022.11.07 |